3.1

Čítače a děliče frekvence

Definice

Jako čítač obecně označujeme obvod, který čítá požadované výskyty (vlastnosti) vstupního signálu (sekvence).

Obvykle tedy čítače čítají hrany (vzestupné či sestupné) periodického hodinového signálu, lze však obecně čítat i jiné parametry signálu nebo i libovolného, neperiodického vstupu.

Čítače mohou čítat v různém kódu, nejen binárním. Výstupem čítače tak může být hodnota např. v Grayově kódu, různých váhových kódech, v decimálním vyjádření apod.

Čítače nemusí vždy jen přičítat (čítat vzestupně), ale mohou i odečítat (čítat sestupně) nebo lze volbu směru čítání ponechat na stavu k tomu určeného řídicího vstupu.

Definice

Binární čítače označujeme jako čítače modulo n – kde n - 1 je nejvyšší hodnota, kterou může čítač načítat. Rozsah čítače je pak určen od 0 do n - 1.

Pro realizaci binárního čítače modulo n je potřeba

klopných obvodů JK či D. Tedy horní celou část dvojkového logaritmu z n. Např. tedy pro realizaci binárního čítače modulo 4, čítajícího v rozsahu: 0, 1, 2, 3 (binárně 00, 01, 10 a 11), jsou potřeba dva klopné obvody JK či D.

V dalším výkladu se zaměříme na čítače hran periodického hodinového signálu Clock (Clk), které patří zdaleka k nejčastějším. Z hlediska distribuce signálu Clock rozlišujeme čítače na synchronní a asynchronní.

Definice

Synchronní čítač je obecně takový čítač, ve kterém je vstupní hodinový signál Clock přímo připojen do vstupů Clk všech jeho klopných obvodů. V ideálním případě by tedy všechny klopné obvody čítače měly překlápět ve stejný časový okamžik, tedy synchronně.

Asynchronní čítač je naopak takový, ve kterém jsou klopné obvody zapojeny z hlediska distribuce hodinového signálu Clock za sebou do kaskády. Ke zdroji Clock je tak připojen pouze první klopný obvod, hodinový vstup každého dalšího je pak zapojen vždy do výstupu předchozího obvodu. Se změnou stavu hodinového signálu Clock tedy překlopí pouze první klopný obvod, druhý překlopí až se změnou výstupu prvního, třetí překlopí, až proběhne změna na výstupu předchozího druhého, a tak dále.

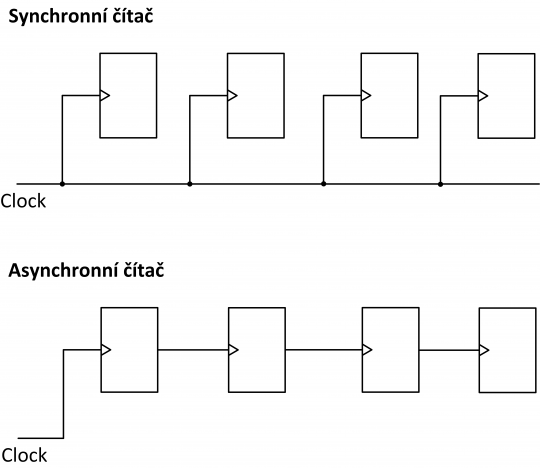

Principiálně lze tento rozdíl zakreslit jako na následujícím obrázku 25.

+

Obr. 25. Principiální rozdíl v zapojení synchronního a asynchronního čítače.

Obě uvedená zapojení čítačů mají své výhody i nevýhody.

Výhody

Výhodou synchronního způsobu zapojení čítače je rychlost překlopení jeho klopných obvodů, a tím pádem i rychlost ustálení správné výstupní hodnoty čítače, neboť v ideálním případě by všechny klopné obvody měly překlopit ve stejný okamžik.

Hlavní výhodou asynchronní realizace čítače je jednoduchost jeho zapojení, jak si uvedeme dále. Nejčastěji totiž realizujeme čítače čítající v binárním kódu (ať již vzestupně nebo sestupně), pro které kromě klopných obvodů zapojených asynchronním způsobem není již potřeba doplňovat žádná jiná hradla ani logické obvody.

Nevýhody

Mezi nevýhody synchronního zapojení čítače patří zejména nutnost použít dodatečná logická hradla, pokud požadujeme realizaci čítače čítajícího postupně v binárním (ale i jiném) kódu. Konkrétní zapojení si uvedeme dále, ale je zřejmé, že pro jednotlivé postupné hodnoty čítání je potřeba ošetřit, kdy mají jednotlivé klopné obvody správně překlápět, aby se na výstupu čítače objevila požadovaná hodnota.

Hlavní nevýhodou asynchronní realizace čítače je kumulace zpoždění, a z toho vyplývající potřebná doba k ustálení správné výstupní hodnoty čítače. Situaci si dále podrobně rozvedeme, ale je zřejmé, že překlopení klopných obvodů čítače, které vyvolá změna vstupního signálu Clock, se postupně šíří od vstupu k výstupu čítače a s každým klopným obvodem v jeho zapojení se celkové zpoždění překlopení a ustálení výstupu čítače zvyšuje.

Poznámka

Čítače také často obsahují dodatečné vstupy pro jejich další řízení. Hojně se tak uplatní asynchronní vstupy klopných obvodů, které lze výhodně použít pro asynchronní nulování čítače nebo pro nastavení výchozí hodnoty čítání. Dále se často můžeme setkat s použitím blokovacího vstupu E (enable), kterým lze vyřadit funkci čítače stejně jako v případě multiplexorů a dalších kombinačních obvodů, viz předchozí text „Kombinační logické obvody a hazardy v kombinačních obvodech“. Rovněž je možné do zapojení čítačů přidat např. řídicí vstup pro změnu směru čítání (přičítání či odčítání) apod.

3.1.1

Asynchronní binární čítač

Pro realizaci základního asynchronního binárního čítače využijeme tzv. dělič 2. Jedná se o sekvenční logický obvod, který frekvenci vstupního hodinového signálu Clock vydělí dvěma, neboli zdvojnásobí jeho periodu na svém výstupu.

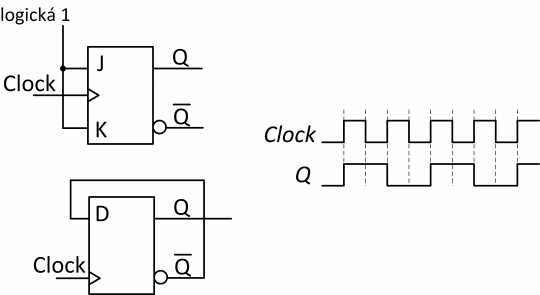

Vyjděme z následující úvahy. Pro realizaci takového děliče bychom využili klopný obvod, který při každé vzestupné (sestupné) hraně hodinového signálu překlopí svůj výstup do opačné hodnoty. Nabízí se využít klopný obvod JK provádějící klopnou transformaci, když oba vstupy J = K = 1. Klopný obvod D klopnou transformaci nerealizuje, ale můžeme využít jeho negovaný výstup

a pomocí zpětné vazby na něj připojit vstup D. Pak bude na jeho výstupu

střídavě hodnota 1 a 0 při každé aktivní hraně hodinového vstupu Clock. Obě uvedená zapojení s průběhem na výstupu

klopného obvodu JK i D v porovnání se vstupem Clock shrnuje obrázek 26.

+

Obr. 26. Princip zapojení děliče 2 pomocí klopného obvodu JK a pomocí klopného obvodu D.

Vytvořené zapojení děliče 2 můžeme nyní využít pro realizaci asynchronního čítače. Stačí si uvědomit, že zapojíme-li další stupně děliče 2 kaskádně za sebe, bude na výstupu každého dalšího signál s poloviční frekvencí (dvojnásobnou periodou) oproti předchozímu vstupu. Vyvedením jednotlivých výstupů

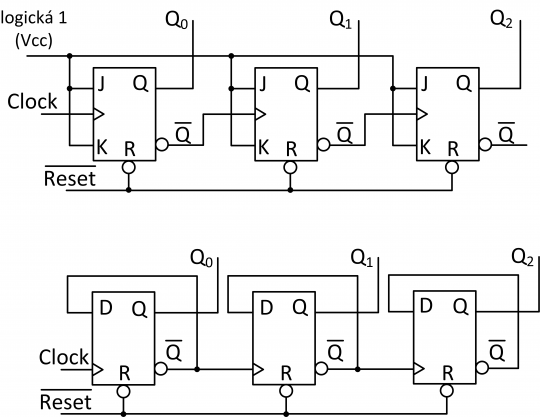

takto kaskádně zapojených klopných obvodů získáme jednotlivá n-bitová řádová místa n-bitového čítače. Uveďme pro příklad na obrázku 27 zapojení čítače modulo 8 čítajícího v intervalu: 0 (000), 1 (001), 2 (010), 3 (011), 4 (100), 5 (101), 6 (110) a 7 (111). Čítač doplníme o asynchronní nulování a uvedeme realizaci z klopných obvodů JK i D.

+

Obr. 27. Realizace asynchronního čítače modulo 8 pomocí klopných obvodů JK i D.

Poznámka

V zapojení asynchronního čítače pomocí klopných obvodů JK připojíme vstupy J i K k trvalé hodnotě logická 1, což v případě pozitivní logiky obvykle představuje kladné napětí Vcc (jeho hodnota je dána typem použitých obvodů).

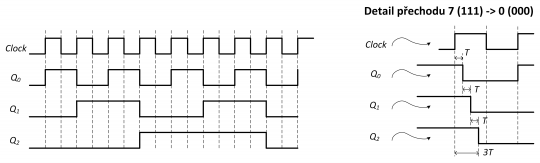

Abychom se přesvědčili, že takto realizovaný čítač správně čítá např. vzestupné hrany vstupního hodinového signálu Clock, provedeme simulaci jeho zapojení (respektive obou – jak zapojení pomocí JK, tak pomocí klopných obvodů D). Výsledek simulace zobrazuje obrázek 28, v pravé části je zachycen detail přechodu čítače ze stavu 7 (111) zpět do stavu 0 (000).

+

Obr. 28. Časové průběhy na jednotlivých třech výstupech asynchronního čítače modulo 8 a detail přechodu ze stavu 7 (111) do stavu 0 (000).

Jak jsme uvedli v předchozím úvodu kapitoly o čítačích, kaskádním zapojením klopných obvodů asynchronního čítače dochází ke kumulaci jeho celkového zpoždění.

Definice

Uvažujeme-li, že každý klopný obvod překlopí se zpožděním T, potom platí, že pro n-bitový asynchronní čítač bude celkové zpoždění pro ustálení jeho výstupu rovno

.

Nevýhody

Dlouhá doba zpoždění (ustálení) výstupu asynchronního čítače představuje jeho největší nevýhodu. Doba zpoždění narůstá s počtem bitů čítače (počtem zapojených klopných obvodů) a značně omezuje praktickou využitelnost asynchronních čítačů.

Pokud totiž nastane situace, že se na vstupu čítače objeví další aktivační hrana hodinového signálu Clock ještě dříve, než všechny klopné obvody v čítači stihnou překlopit na předchozí aktivační hranu, dostane se čítač do nestabilního stavu, a jeho výstup se tak nikdy zcela neustálí a nelze z něho odečíst správnou hodnotu. Tento jev se v literatuře označuje jako tzv. ripple-effect a pro jeho vznik platí podmínka:

,

kde TClock představuje periodu vstupního hodinového signálu Clock, n vyjadřuje počet bitů (klopných obvodů) čítače a T dobu zpoždění jednoho klopného obvodu. Použitelnost asynchronního čítače záleží tedy na konkrétní aplikaci, respektive na vzájemném vztahu periody čítaného hodinového signálu a celkového zpoždění čítače.

Výhody

Předností asynchronního čítače je skutečnost, že si pro jeho realizaci vystačíme pouze s danými klopnými obvody a není potřeba doplňovat další logická hradla. To má samozřejmě výhodu v levnější a snazší realizaci, menší ploše obvodu (např. v poli FPGA) i nižší spotřebě čítače.

I proto mohou asynchronní čítače nalézt uplatnění v řadě nenáročných aplikací. Z tohoto důvodu je lze rovněž nalézt přímo integrované v několika obvodech řady 7400. Nejčastěji jde o obvod 74HC(T)93, čtyřbitový asynchronní čítač realizovaný technologií High-speed CMOS (případně i kompatibilní s TTL úrovněmi), nebo obvod 74HC(T)4024, sedmibitový asynchronní čítač v téže technologii, či obvod 74HC4040, dvanáctibitový asynchronní čítač opět v technologii High-speed CMOS.

3.1.2

Synchronní binární čítač

Obecný návrh a realizace synchronního čítače je značně komplexní a uvedeme si zde jen zjednodušený principiální návrh. Obecný návrh synchronního čítače lze nalézt zpracovaný v různé literatuře, např. v [6].

Jak jsme si uvedli výše, v případě synchronního čítače jsou všechny jeho klopné obvody připojeny přímo ke zdroji hodinového signálu Clock. Pokud však chceme vytvořit čítač čítající v binárním kódu a přičítající (odečítající) jedničku při každé aktivační hraně Clock, je potřeba v tomto případě použít dodatečná logická hradla. U asynchronního čítače jsme zajistili podmínku, že následující klopný obvod čítače smí překlopit, až pokud na výstupech všech předchozích klopných obvodů je hodnota logická 1 tím, že jsme klopné obvody navzájem propojili pomocí jejich hodinových vstupů a výstupů. V případě synchronního čítače tedy musíme tuto podmínku zajistit doplněním dodatečných logických hradel do datových vstupů klopných obvodů, neboť hodinové vstupy jsou přímo připojeny k hodinovému signálu Clock.

Pro porovnání si znovu uvedeme realizace čítače modulo 8 pomocí klopných obvodů JK a pomocí D, tentokrát však ve variantě synchronní, opět s asynchronním nulováním. Nejprve si prohlédněme realizaci pomocí klopných obvodů JK na obrázku 29.

+

Obr. 29. Zapojení synchronního čítače modulo 8 pomocí klopných obvodů JK.

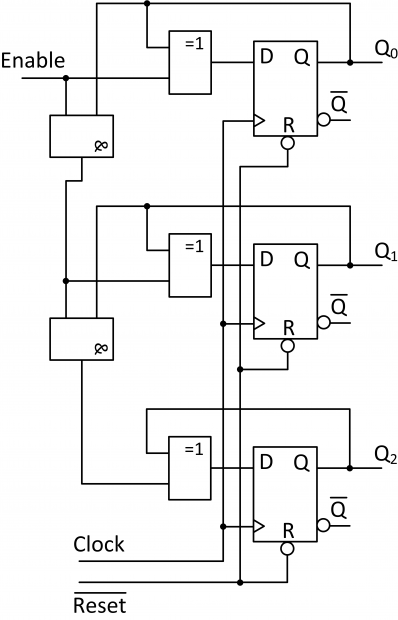

Jak vyplývá z obrázku 29, bylo nutno použít dodatečně hradlo logického součinu AND, abychom zajistili, že třetí klopný obvod JK překlopí až v okamžiku, kdy se na výstupu předchozích dvou objeví hodnota logická 1. Nyní si uveďme i realizaci téhož čítače pomocí klopných obvodů D, kdy jej doplníme ještě o blokovací vstup Enable. Výsledná realizace je uvedena na obrázku 30.

+

Obr. 30. Zapojení synchronního čítače modulo 8 pomocí klopných obvodů D.

Pro realizaci čítače pomocí klopných obvodů D potřebujeme doplnit hradla neekvivalence, XOR, do zpětné vazby každého klopného obvodu D. Ta jsou nutná, aby při příchodu každé aktivační hrany hodinového signálu Clock došlo porovnáním předchozí a současné hodnoty na výstupu každého klopného obvodu D k jeho případnému překlopení. Současně jsme doplnili i součinová hradla AND pro blokovací vstup Enable, jehož aktivací je potřeba čítač spustit a dále jeho držením na hodnotě logická 1 pokračovat v čítání.

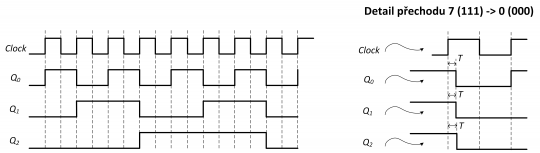

Pro porovnání funkce obou typů čítačů si zobrazme opět časový průběh na jednotlivých výstupech synchronního čítače modulo 8 při jeho přechodu ze stavu 7 (111) zpět do stavu 0 (000), viz obrázek 31.

+

Obr. 31. Časový průběh na jednotlivých výstupech synchronního čítače modulo 8 a detail přechodu ze stavu 7 (111) zpět do stavu 0 (000).

Z porovnání detailu přechodu pro asynchronní čítač (obrázek 28) a synchronní čítač (obrázek 31) je patrný rozdíl.

Definice

Doba zpoždění ideálního synchronního čítače je rovna T, kde T je doba zpoždění jednoho jeho klopného obvodu. Doba zpoždění ideálního synchronního čítače tak nezávisí na počtu jeho bitů (počtu klopných obvodů).

Poznámka

Ve skutečnosti ani u synchronních čítačů nedochází k překlopení všech jejich klopných obvodů ve stejném okamžiku. Kromě zpoždění vlastních klopných obvodů se totiž uplatní i zpoždění vlivem šíření signálů jednotlivými cestami, v tomto případě šíření hodinového signálu Clock. Jak je patrné ze všech obrázků s realizacemi synchronních i asynchronních čítačů výše, cesta hodinového signálu k jednotlivým klopným obvodům čítače je různá a zapříčiní vznik dodatečného zpoždění. To je však vzhledem ke zpoždění překlopení vlastních klopných obvodů řádově mnohem menší a lze jej často zanedbat. I tak však způsobí drobné časové odchylky v okamžiku překlopení klopných obvodů synchronního i asynchronního čítače.

Nevýhody

Jak je patrné z porovnání realizace synchronního a asynchronního čítače výše, při zapojení synchronní varianty je vždy potřeba doplnit dodatečná logická hradla, v uvedeném příkladu čítače modulo 8 to je buď jedno hradlo v případě použití klopných obvodů JK, nebo pět hradel v případě klopných obvodů D. To má samozřejmě nevýhodu ve zvýšení složitosti zapojení se všemi z toho vyplývajícími negativy.

Výhody

Výhodou synchronního čítače oproti asynchronní variantě je především krátká doba jeho celkového zpoždění (ustálení), která navíc v ideálním případě není závislá na počtu bitů čítače.

Poznámka

Synchronní čítače patří k často využívaným sekvenčním logickým obvodům v celé řadě nejrůznějších aplikací. I proto lze nalézt množství obvodů řady 7400 přímo s integrovanými čítači v nejrůznějších úpravách a parametrech. Namátkou uveďme obvod 74LS68 (74LS69), 2× čtyřbitový synchronní čítač umožňující využití jako binární i jako dekadický čítač v řadě Low-power Schottky TTL, nebo 74LS90 (74LS92, 74LS93), vždy 1× synchronní čítač (čtyřbitový, dekadický, děleno 12) opět v řadě Low-power Schottky TTL, či série obvodů 74LS160, 74LS161, 74LS162 a 74LS163, což jsou vše 1× čtyřbitové synchronní čítače s asynchronním přednastavením a synchronním či asynchronním nulováním, všechny realizované pomocí Low-power Schottky TTL.

3.1.3

Děliče frekvence

Jako dělič frekvence (či frekvenční děličku) označujeme obvod, kterým upravujeme periodu vstupního periodického hodinového signálu tak, abychom na výstupu získali signál s jinou (vydělenou) periodou.

Poznámka

Jedná se o častý případ, kdy je různé části obvodu potřeba taktovat jiným hodinovým signálem nebo je nezbytné zajistit komunikaci s vnějšími periferiemi s využitím různých hodinových signálů. V tom případě z jednoho zdroje hodinového signálu s danou periodou získáme jeho vydělením potřebné hodinové signály s různými požadovanými periodami.

Dělič frekvence není ve své podstatě nic jiného než čítač čítající požadované hrany zdrojového hodinového signálu. Při načítání požadovaného počtu těchto hran, vygenerujeme na jeho výstupu hodinový signál s požadovaným poměrem periody vůči zdrojovému vstupnímu signálu.