2.1

Multiplexor a demultiplexor

Multiplexory a demultiplexory jsou v praxi hojně využívány v řadě aplikací. Lze pomocí nich totiž realizovat i logické funkce [2].

Zajímavost

Pojem multiplexování (opakem je demultiplexování) obecně představuje proces sdružování, například signálů nebo informací apod., do jednoho celku tak, aby je bylo možno opět od sebe jednoznačně oddělit (tedy demultiplexovat).

Typický příklad na využití multiplexace a demultiplexace lze nalézt v telekomunikační technice. Kdy mezi obvykle dvěma vzdálenými místy máme pouze jeden komunikační kanál, ale na vstupu kanálu máme více informačních zdrojů. Na výstupu z komunikačního kanálu pak máme adekvátní počet příjemců informací. Procesem multiplexace, tedy jasně definovaným přiřazováním zdrojů k informačnímu kanálu, přenášíme jejich informace. Na výstupu procesem demultiplexace, se stejně definovaným přiřazováním jako na vstupu, připojujeme ke kanálu přijímače a přenesenou informaci z komunikačního kanálu jim předáváme. Nutnou podmínkou multiplexace/demultiplexace je schopnost rozlišit signály jednotlivých informačních zdrojů. Častým příkladem je frekvenční multiplexování signálů s navzájem rozdílnými frekvencemi, časové multiplexování s oddělenými časovými okamžiky pro vysílání jednotlivých stanic nebo například vlnové multiplexování v případě optických telekomunikací a přenosu optických signálů s různými vlnovými délkami.

Definice

V základním přiblížení tedy jako multiplexor chápeme kombinační logický obvod, který obsahuje obecně n datových vstupů (n je obvykle mocnina 2), log2(n) adresových vstupů a jeden výstup. Pomocí hodnoty (kombinace hodnot) na adresovém vstupu a je určeno, který z datových vstupů je přepnut do výstupu multiplexoru [2].

Multiplexor si tak můžeme zjednodušeně představit jako programovatelný přepínač, který ovládáme adresovým vstupem (vstupy), podle nějž vybíráme datový signál, který je přepnut do výstupu [3].

Demultiplexor je pak přesně opačným obvodem. Tedy opět pomocí hodnoty jeho adresového vstupu (vstupů) přepínáme, do kterého z n výstupů demultiplexoru je připojen jeden jeho vstup [3].

Poznámka

Protože ve dvouhodnotové logice dokážeme adresovat pomocí jednoho adresového vstupu dva datové vstupy (jeden má adresu logická 1 a druhý logická 0), je optimální, aby multiplexor pro a adresových vstupů měl 2a datových vstupů n.

V praxi se tedy můžeme setkat s multiplexory (kombinačními logickými obvody): 2 na 1 (dva datové vstupy, jeden adresový), 4 na 1 (čtyři datové vstupy, dva adresové), 8 na 1 (osm datových vstupů, tři adresové) atd.

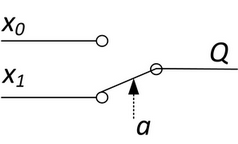

Principiální značku nejjednoduššího multiplexoru 2 na 1 se vstupy x0 a x1, adresovým vstupem a a výstupem Q představuje obrázek 2.

+

Obr. 2. Principiální schéma jednoduchého multiplexoru 2 na 1 jako řízeného přepínače.

Pomocí úplné pravdivostní tabulky můžeme tento nejjednodušší multiplexor popsat tak, že máme-li na adresovém vstupu a hodnotu logická 0, je do výstupu multiplexoru přepnut vstup x0 (výstup Q kopíruje hodnotu x0), zatímco ve stavu adresového vstupu a logická 1 je do výstupu multiplexoru Q přepnut vstup x1. Úplná pravdivostní tabulka je uvedena v tabulce 1, její zkrácenou verzi s použitím neurčitých stavů druhého vstupu uvádí tabulka 2.

Tabulka 1. Úplná pravdivostní tabulka multiplexoru 2 na 1.

a | x1 | x0 | Q |

0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 0 |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

1 | 1 | 0 | 1 |

1 | 1 | 1 | 1 |

Protože multiplexor reaguje na základě adresového vstupu a vždy jen na jeden ze vstupů x0, x1, můžeme pro druhý z nich v pravdivostní tabulce použít neurčitý stav, a pomocí toho tabulku zjednodušit, jak ukazuje tabulka 2.

Tabulka 2. Zkrácená pravdivostní tabulka multiplexoru 2 na 1.

a | x1 | x0 | Q |

0 | X | 0 | 0 |

0 | X | 1 | 1 |

1 | 0 | X | 0 |

1 | 1 | X | 1 |

Pomocí pravdivostních tabulek můžeme algebraicky vyjádřit rovnici pro výstup multiplexoru Q v disjunktním tvaru jako:

.

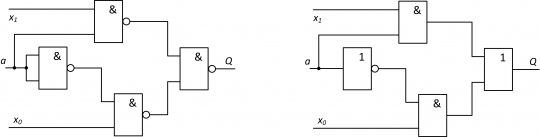

Disjunktní tvar pak můžeme realizovat pomocí hradel NAND dle obrázku 3 vlevo. Obvyklejší je však realizace přímo disjunktního tvaru za použití hradel AND a OR a INV (invertor) jako negace, jak ukazuje obrázek 3 vpravo.

+

Obr. 3. Realizace multiplexoru 2 na 1 pomocí hradel NAND (vlevo) a obvyklá realizace multiplexoru pomocí hradel AND, OR a INV (vpravo).

Zajímavost

V praxi se často do zapojení a realizace multiplexoru přidává tzv. blokovací (řídicí) vstup – E (enable) [3]. Ten slouží k odblokování (povolení) funkce multiplexoru a je obvykle použit v inverzní (negativní) logice [4], tzn., pokud je vstup E ve stavu logická 0, multiplexor pracuje, naopak vstup E ve stavu logická 1 zablokuje činnost multiplexoru. Inverzní logika je použita z toho důvodu, že pro reálný integrovaný obvod s multiplexorem není potřeba na vstup E přivádět napětí (E je uzemněn), pokud má multiplexor fungovat, zatímco pokud chceme multiplexor zablokovat, přivedeme na E kladné napětí odpovídající logické 1.

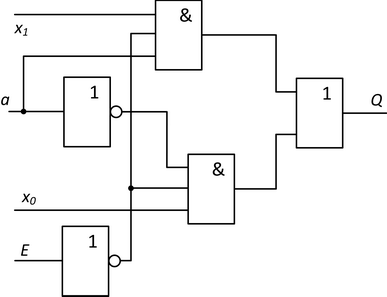

Úpravu multiplexoru a přidání blokovacího vstupu E znázorňuje obrázek 4.

+

Obr. 4. Multiplexor 2 na 1 s blokovacím vstupem E.

Pro přidání blokovacího vstupu E vyměníme původní dvouvstupová hradla AND za třívstupová. Z inverzní logiky a pravdivostní tabulky hradla AND vyplývá, že pokud na vstupu E bude hodnota logická 1, bude na výstupu daného hradla vždy hodnota logická 0 nezávisle na hodnotě datového vstupu x0, x1 i adresového vstupu a. Na výstupu multiplexoru Q pak bude trvale hodnota logická 0.

Upravená rovnice pro vyjádření výstupu multiplexoru Q s blokovacím vstupem E pak bude:

.

Zajímavost

Protože jsou multiplexory často využívány v praxi v nejrůznějších logických obvodech, existují rovněž integrované obvody TTL (Transistor–transistor logic) i CMOS (Complementary metal–oxide–semiconductor) s již hotovými multiplexory a není tedy potřeba je zapojovat z jednotlivých hradel NAND, AND či OR [4]. Multiplexor 2 na 1 s blokovacím vstupem tak v katalogu například nalezneme jako integrovaný obvod 74LS157 – 4× v jednom pouzdře multiplexor 2 na 1 realizovaný technologií TTL v řadě Low-power Schottky – nebo například 74HC157 (či 74HCT157) – opět 4× v jednom pouzdře multiplexor 2 na 1 realizovaný tentokráte technologií CMOS, konkrétně v řadě High speed či High speed kompatibilní s úrovněmi TTL.

V úvodu jsme zmínili, že multiplexory mají obecně n datových vstupů, kde n je obvykle mocnina 2. V praxi se tak často používají i multiplexory 4 na 1 či 8 na 1 a další. Představíme si proto ještě v krátkosti multiplexor 4 na 1. Tento multiplexor má tedy čtyři datové vstupy x0, x1, x2, x3, mezi kterými přepínáme pomocí dvojice adresových vstupů a0, a1 do výstupu Q. Uveďme si nejprve zkrácenou pravdivostní tabulku tohoto multiplexoru v tabulce 3.

Tabulka 3. Zkrácená pravdivostní tabulka multiplexoru 4 na 1.

a1 | a0 | x3 | x2 | x1 | x0 | Q |

0 | 0 | X | X | X | 0 | 0 |

0 | 0 | X | X | X | 1 | 1 |

0 | 1 | X | X | 0 | X | 0 |

0 | 1 | X | X | 1 | X | 1 |

1 | 0 | X | 0 | X | X | 0 |

1 | 0 | X | 1 | X | X | 1 |

1 | 1 | 0 | X | X | X | 0 |

1 | 1 | 1 | X | X | X | 1 |

Pomocí dvojice adresových vstupů a0, a1, které si můžeme představit jako dvoubitovou vstupní kombinaci (00, 01, 10 a 11), vybíráme jeden ze čtyř vstupů x0, x1, x2, x3, který bude přepnut do výstupu Q. Algebraicky tak můžeme výstup multiplexoru zapsat:

.

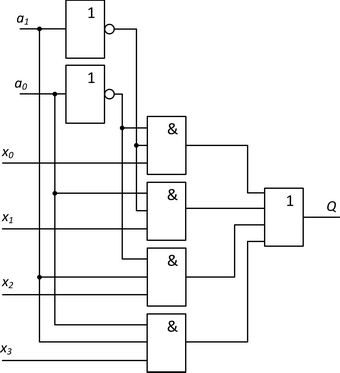

Zapojení multiplexoru 4 na 1 pomocí hradel AND, OR a INV představuje obrázek 5.

+

Obr. 5. Zapojení multiplexoru 4 na 1 s použitím hradel AND, OR a INV.

Stejným způsobem, jako v předchozím případu multiplexoru 2 na 1, lze i do multiplexoru 4 na 1 doplnit blokovací vstup E. Jeho negace (E je znovu chápán v inverzní logice) je opět připojena do vstupů jednotlivých součinových hradel, která jsou pak tím pádem čtyřvstupová, pro jejich případné blokování [4].

Zajímavost

Stejně jako multiplexor 2 na 1 i multiplexor 4 na 1 je k dispozici přímo v integrovaném obvodu. V katalogu ho lze najít pod označením např. 74LS153 – 2× v jednom pouzdře multiplexor 4 na 1 realizovaný technologií TTL v řadě Low-power Schottky – nebo znovu adekvátně k němu 74HC153 (či 74HCT153) – opět 2× v jednom pouzdře multiplexor 4 na 1 realizovaný technologií CMOS v řadě High speed či High speed kompatibilní s úrovněmi TTL.

Multiplexor 8 na 1 nalezneme v katalogu součástek jako integrovaný obvod 74LS151 nebo například 74HC151 (či 74HCT151) – 1× v jednom pouzdře multiplexor 8 na 1 opět buď v provedení TTL, či CMOS jako výše multiplexory 2 na 1 a 4 na 1.

Ve stručnosti se zmíníme rovněž o demultiplexoru. Jedná se o funkčně opačný obvod, než je multiplexor [4].

Definice

Z jednoho datového vstupu demultiplexoru x je tedy na základě stavu adresového vstupu a přepínán signál do jednoho z výstupů Q. Přičemž tentokráte platí, že počet výstupů Q je obvykle roven mocnině 2 a počet adresových vstupů je pak dvojkový logaritmus počtu výstupů Q. Pokud je tedy n výstupů Q (Q0, Q1, …, Qn-1), pak adresových vstupů a je právě log2(n). V praxi se tak můžeme nejčastěji setkat s demultiplexory 1 na 2, 1 na 4, 1 na 8, 1 na 16 atd.

Demultiplexor plní opačnou funkci k multiplexoru a můžeme si jej zjednodušeně představit jako programovatelný přepínač, který opět ovládáme adresovým vstupem (vstupy), podle nějž směrujeme jeden vstupní datový signál do zvoleného výstupu demultiplexoru [5].

Pomocí pravdivostní tabulky můžeme popsat demultiplexor 1 na 2 (viz tabulka 4) a demultiplexor 1 na 4 (viz tabulka 5).

Tabulka 4. Pravdivostní tabulka demultiplexoru 1 na 2.

a | x | Q1 | Q0 |

0 | 0 | 0 | 0 |

0 | 1 | 0 | 1 |

1 | 0 | 0 | 0 |

1 | 1 | 1 | 0 |

Protože má demultiplexor 1 na 2 celkem dva výstupy Q0, Q1, zapíšeme pro každý z nich samostatné algebraické vyjádření:

,

.

Tabulka 5. Pravdivostní tabulka demultiplexoru 1 na 4.

a1 | a0 | x | Q3 | Q2 | Q1 | Q0 |

0 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 0 | 0 | 1 |

0 | 1 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 0 | 1 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 0 | 0 | 0 |

Obdobně pro demultiplexor 1 na 4 je potřeba soustava čtyř algebraických výrazů, každý pro jeden výstup Q0, Q1, Q2, Q3:

,

,

,

.

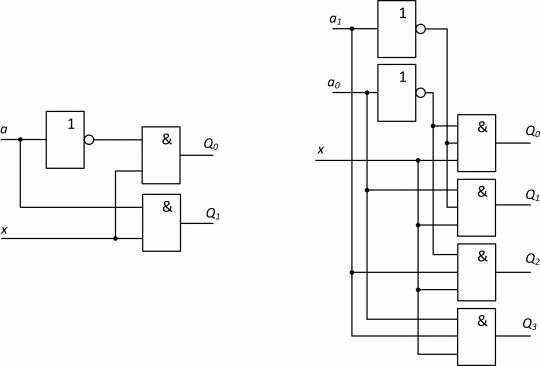

Realizace obou demultiplexorů pomocí hradel AND, OR a INV je ilustrována na obrázku 6, ve kterém je demultiplexor 1 na 2 v levé části, zatímco vpravo je demultiplexor 1 na 4.

+

Obr. 6. Demultiplexory 1 na 2 (vlevo) a 1 na 4 (vpravo) realizované pomocí hradel AND, OR a INV.

Poznámka

Demultiplexory lze rovněž vybavit blokovacím E (enable) vstupem, kterým stejně jako v případě multiplexorů můžeme zablokovat všechna součinová hradla, a tím celý demultiplexor [5].

Zajímavost

S ohledem na časté využití v nejrůznějších logických obvodech jsou také některé demultiplexory k dispozici přímo jako integrované obvody. V katalogu tak například nalezneme obvod 74LS155, který představuje 2× v jednom pouzdře demultiplexor 1 na 4 s invertovanými výstupy realizovaný v technologii TTL řady Low-power Schottky, dále např. obvod 74LS154, což je 1× v jednom pouzdře demultiplexor 1 na 16 v téže technologii apod.