11.1

Posuvné registry

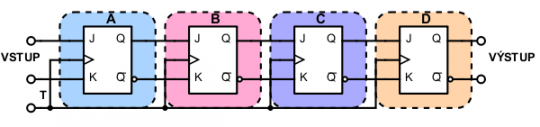

Posuvný registr je možno sestavit z klopných obvodů JK spojených za sebou tak, že výstupy Q,

jsou vždy připojeny na vstupy J, K dalšího klopného obvodu. Všechny klopné obvody jsou řízeny synchronně taktovacími (hodinovými) impulzy. Informace načtená přes vstupy J, K do klopného obvodu při nástupní hraně taktovacího impulzu je každým dalším taktovacím impulzem posunuta o jeden klopný obvod dále. Proto se uvedený registr jmenuje posuvný registr. Po čtyřech taktech se přesune informace ze vstupu na výstup registru.

+

Obr. 92. Čtyřbitový posuvný registr-schéma

+

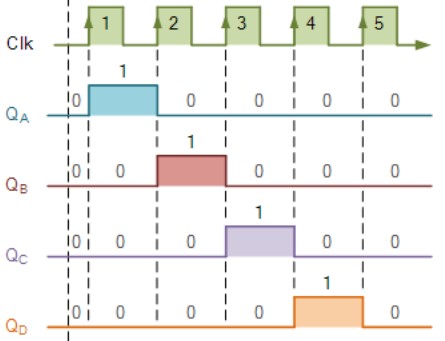

Obr. 93. Čtyřbitový posuvný registr-časový diagram

11.1.1

Posuvný registr se sériovým vstupem a sériovým výstupem

+

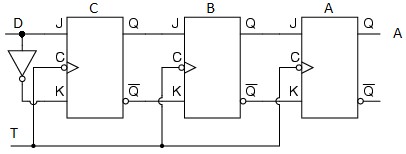

Obr. 94. Posuvný registr se sériovým vstupem a sériovým výstupem-schéma

V zapojení na obrázku jsou použity klopné obvody JK s výstup Q a

. Na vstupu D vstupují data s frekvencí taktovacího signálu. Třemi taktovacími impulzy se data přenesou ze vstupu D na výstup A. V dalším taktu je výstup A přepsán dalšími daty.

+

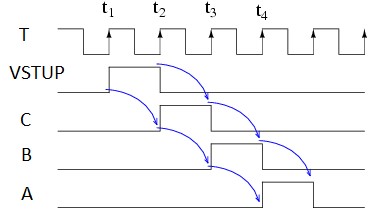

Obr. 95. Posuvný registr se sériovým vstupem a sériovým výstupem-časový diagram

V hodinovém čase t1 jsou data ve všech třech stupních rovna 0. To platí i pro stupeň C, kde výstup bude rovnat 1 až v čase t2. V čase t3 dochází k přepisu dat (1) do stupně B. V dalším taktu (t4) dojde k přepisu dat na výstup stupně A. Tímto způsobem (sériově) se neustále přepisují data za vstupu na výstup tohoto posuvného registru.

11.1.2

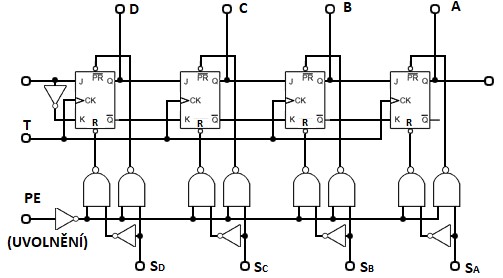

Posuvný registr s paralelním vstupem a paralelním výstupem

Čtyřbitového posuvný registr s klopnými obvody JK je opatřen vstupy R (pro nulování a vstupy S (vstupy pro nastavení do stavu 1). Pomocí vstupů SA, SB, SC a SD se nastavují přes hradla NAND data v klopných obvodech bez taktovacích pulzů potřebných pro sériové plnění. Data jsou z paralelních vstupů uvolňována (propojována) na vstupy JK klopných obvodů signálem 1 na vstupu PE uvolnění vstupu paralelní předvolby (Paralel Enable). V registrech uvedeného typu je posuv dat blokován stavem PE=0.

+

Obr. 96. Posuvný registr s paralelním vstupem a paralelním výstupem-schéma

11.1.3

Paralelně-sériový převodník

Paralelně-sériový převodník uloží do paměti paralelně načtená data a pak tato data vysílá sériově bit po bitu. Paralelně-sériový převodník lze realizovat pomocí paralelně nastavovaného posuvného registru. Pro převod prostorově rozprostřeného signálu (paralelního přenosu po více vodičích) na časově rozprostřený signál (sériový přenos po jednom vodiči) se v přenosové a spojovací technice používají paralelně-sériové převodníky. (K přenosu 8bitových paralelních dat v časově multiplexním sériovém režimu po jednom vodiči). K takovému přenosu je třeba 8násobný kmitočet, tedy i přenosová cesta, která takový signál přenese.

11.1.4

Sériově-paralelní převodník

Při sériově-paralelním převodu jsou postupně přijímané bity ukládány do paměti tak, aby vytvářely vícebitová (např. 8bitová) slova, která jsou předávána dále najednou po více vodičích, tedy paralelně. Sériově-paralelní převod může být realizován pomocí integrovaného sériově-paralelního posuvného registru. V oblastech přenosové a spojovací techniky je často potřeba převést sériově přenášená data na paralelní tvar, a to kvůli ukládání a zpracování po slovech (v počítačích) nebo kvůli snížení přenosové rychlosti (kmitočtu přenosového signálu). Data jsou tedy převáděna z časového multiplexu na prostorový multiplex (prostorové rozprostření na více vodičů).