10.1

Asynchronní čítač

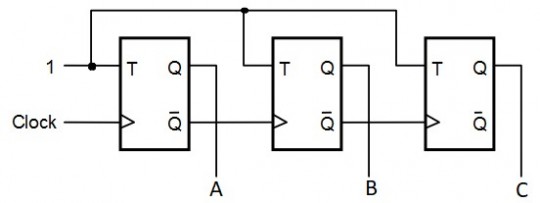

Čítač je sestaven ze tří klopných obvodů T zapojených za sebou. Doba zpracování signálu v asynchronním čítači je dána součtem zpoždění na jednotlivých klopných obvodech čítače. Sestupná hrana prvního taktovacího impulzu překlopí první klopný obvod. Každá sestupná hrana výstupu A překlopí klopný obvod B. Každá sestupná hrana výstupu B překlopí obvod C atd.

+

Obr. 83. Asynchronní čítač

+

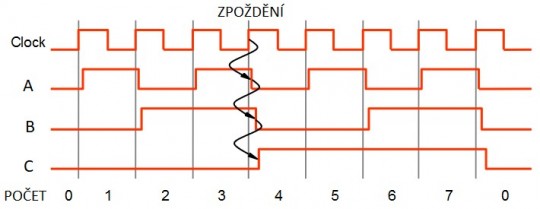

Obr. 84. Asynchronní čítač-časové průběhy

+

Obr. 85. Asynchronní čítač-pravdivostní tabulka

Zpětný čítač lze sestavit podobně jako dopředný čítač s tím rozdílem, že pro přenos do dalšího klopného obvodu T je používán negovaný výstup

.

10.1.1

Asynchronní 4bitový BCD čítač

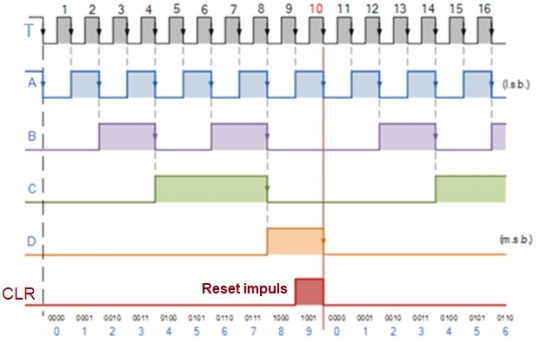

Asynchronní 4bitový BCD čítač (Čítače s deseti stavy jsou označovány jako čítače BCD). Na obrázku je schéma zapojení se čtyřmi klopnými obvody JK a součinovým hradlem, které při stavu 10012=9 vynuluje všechny čtyři klopné obvody signálem 0 na vstupech

.

+

Obr. 86. Asynchronní 4bitový BCD čítač s JK klopnými obvody

Pro načítání od 0 do 9 jsou zapotřebí čtyři klopné obvody, které však umožňují načítání od 0 až do 15. Má-li se čítač po deseti vstupních impulzech vracet do počátečního stavu, tj. počítat jen do 9, musí stav 10 identifikovat a čítač nastavit do výchozího stavu. Třívstupové hradlo NAND má na výstupu logickou 0 v případě, že jsou všechny tři vstupy rovny log 1. Tento stav nastane, když je A=1, D=1 (10012 = 910) a hodinový signál bude mít také hodnotu log 1. V tomto okamžiku dojde k vynulování všech výstupů (A, B, C, D) a čítač začne opět počítat od nuly.

+

Obr. 87. Asynchronní 4bitový BCD čítač-časové průběhy