9.2

Klopný obvod D

+

Obr. 71. Klopný obvod D – schématická značka

+

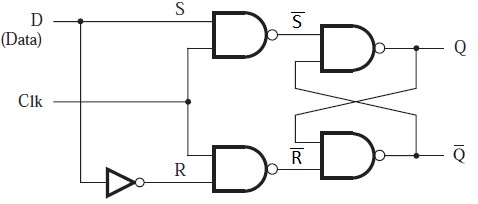

Obr. 72. Klopný obvod D – zapojení bez nulování

Klopný obvod D je klopný obvod RS s řídicím hodinovým vstupem, rozšířený ještě o datový vstup D (Data latch=blokování dat, nebo Delay=prodleva při přenosu dat), který je v nezměněné podobě přiveden na vstup S a v invertované podobě přiveden na vstup R. Klopný obvod D se dvěma vstupy nemá neurčitý stav, protože jen jedno ze vstupních hradel NAND může mít na výstupu 0. Na vstupech

,

vlastního klopného obvodu může být tedy jen jeden řídicí signál 0, a to po dobu trvání hodinového impulzu (C=1), který umožní uložení dat (stavu na datovém vstupu D) do klopného obvodu a přenesení těchto dat na výstup Q.